数字延迟发生器 DG645 — 低抖动延迟发生器 -

4个脉冲输出 -

8 个延迟输出(可选) -

小于 25 ps rms 抖动 -

触发率高达 10 MHz -

准确率发生器 -

快速过渡时间 -

Ovenized 或 Rb 时基(可选) -

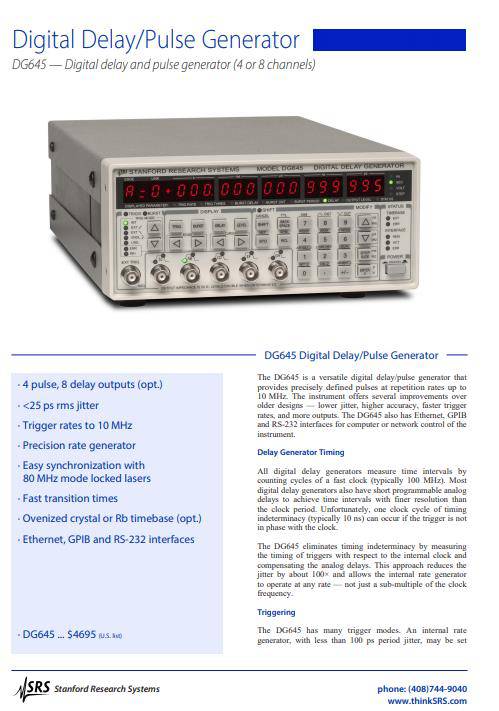

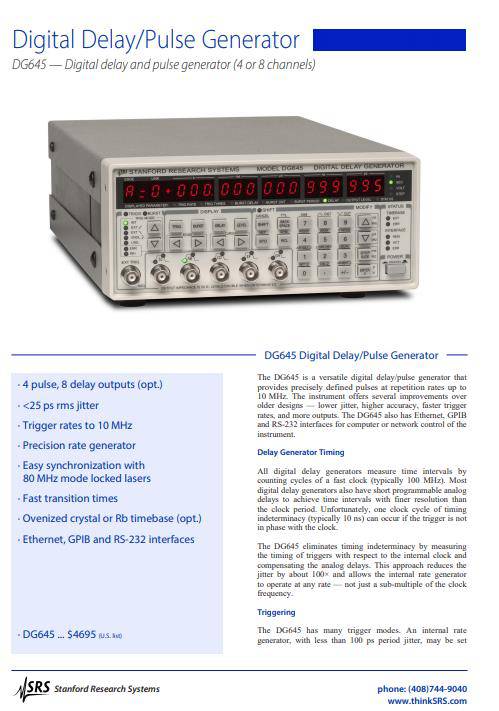

以太网、GPIB 和 RS-232 概述: | DG645 是一款多功能数字延迟/脉冲发生器,可提供准确定义的脉冲,重复频率高达 10 MHz。与旧设计相比,该仪器提供了多项改进——更低的抖动、更高的精度、更快的触发速率和更多的输出。DG645 还具有以太网、GPIB 和RS-232接口,用于仪器的计算机或网络控制。 | 规格: | DG645 规格 | | 延误 | | 频道 | 4 个独立脉冲控制位置和宽度。8 个延迟通道可供选择。

(见下面的输出选项) | | 范围 | 0 到 2000 | | 解析度 | 5 皮 | | 准确性 | 1 ns + (时基误差 × 延迟) | 抖动 (rms)

分机。触发。到任何输出

T 0到任何输出 |

25 ps + (时基抖动 × 延迟)

15 ps + (时基抖动 × 延迟) | | 触发延迟 | 85 ns(外部触发到 T 0输出) | | 时基 | | 标准水晶 | | | 抖动 | 10 -8/ | | 稳定 | 2 x 10 -6 (20 °C 至 30 °C) | | 老化 | 5 ppm/年 | | 选择。4 OCXO | | | 抖动 | 10 -11/ | | 稳定 | 2 x 10 -9 (20 °C 至 30 °C) | | 老化 | 0.2 ppm/年 | | 选择。5 铷 | | | 抖动 | 10 -11/ | | 稳定 | 2 x 10 -10(20 °C 至 30 °C) | | 老化 | 0.0005 ppm/年 | | 外部输入 | 10 MHz ± 10 ppm,正弦 >0.5 Vpp,

1 kΩ 阻抗 | | 输出 | 10 MHz,2 Vpp 输入 50 Ω | | 外部触发 | | 速度 | DC 至 1/(100 ns + 长延迟)。

10 MHz | | 临界点 | ±3.50 伏直流 | | 坡 | 在上升沿或下降沿触发 | | 阻抗 | 1 兆欧 + 15 pF | | 内部速率发生器 | | 触发模式 | 连拍、线拍或单拍 | | 速度 | 100 µHz 至 10 MHz | | 解析度 | 1 微赫兹 | | 准确性 | 与时基相同 | | 抖动 (rms) | <25 ps(10 MHz/N 触发率)

<100 ps(其他触发率) | | 突发发生器 | 触发到D一个 T 0

范围

分辨率 |

0 到 2000

5 ps | 脉冲之间的周期

范围

分辨率 |

100 ns 至 42.9 s

10 ns | | 每个突发的延迟周期 | 1 至 2 32 - 1 | | 输出(T 0、AB、CD、EF 和 GH) | | 源阻抗 | 50Ω | | 过渡时间 | <2 纳 | | 过冲 | <100 mV + 10 % 的脉冲幅度 | | 抵消 | ±2V | | 振幅 | 0.5 至 5.0 V(电平 + 偏移<6.0 V) | | 准确性 | 100 mV + 5 % 脉冲幅度 | | | | | | | | 一般的 | | 计算机接口 | GPIB (IEEE-488.2)、RS-232 和以太网。所有仪器功能都可以通过接口进行控制。 | | 非易失性存储器 | 可以存储和调用九组仪器配置。 | | 力量 | <100 W,90 至 264 VAC,47 Hz 至 63 Hz | | 方面 | 8.5" × 3.5" × 13" (WHL) | | 重量 | 9 磅。 | | 保修单 | 一年零件和人工材料和工艺缺陷 | | | | | | | | 输出选项 | | | | | 选项 1(延迟输出) | | 输出数量 | 8 个(后面板 BNC) | | 输出 | T 0 , A, B, C, D, E, F, G 和 H | | 源阻抗 | 50Ω | | 过渡时间 | <1 纳 | | 过冲 | <100 毫伏 | | 等 | +5 V CMOS 逻辑 | 脉冲特性

上升沿

下降沿 |

在长延迟后 25 ns 编程延迟 | | 选项 2(高压输出) | | 输出数量 | 8 个(后面板 BNC) | | 输出 | T 0 , A, B, C, D, E, F, G 和 H | | 源阻抗 | 50Ω | | 过渡时间 | <5 纳 | | 别 | 0 至 30 V 进入高阻抗,0 至 15 V 进入 50 Ω(幅度降低 1 %/kHz) | 脉冲特性

上升沿

下降沿 |

在上升沿后 100 ns 的 编程延迟 | | 选项 3(组合输出) | | 输出数量 | 8 个(后面板 BNC) | | 输出 | T 0 , AB, CD, EF, GH, (AB+CD), (EF+GH), (AB+CD+EF), (AB+CD+EF+GH) | | 源阻抗 | 50Ω | | 过渡时间 | <1 纳 | | 过冲 | <100 mV + 10 % 的脉冲幅度 | | 脉冲特性 | | | T 0 , AB, CD, EF, GH | 延迟之间的时间逻辑高 | | (AB+CD), (EF+GH) | 由给定通道的逻辑或创建的两个脉冲 | | (AB+CD+EF) | 由给定通道的逻辑或创建的三个脉冲 | | (AB+CD+EF+GH) | 由给定通道的逻辑或创建的四个脉冲 | | 选项 SRD1(快速上升时间模块) | | 上升时间 | <100 皮 | | 秋季时间 | <3 纳 | | 抵消 | -0.8 V 至 -1.1 V | | 振幅 | 0.5V 至 5.0V | | 加载 | 50Ω | | | |

原创作者:深圳奥德赛创精密仪器有限公司

标签:DG645数字延迟发生器 超低抖动延迟发生器 美国SRS发生器

|